前言

最近老師上課複習了計算機組織中CPU執行指令的過程等內容,此篇整理一下

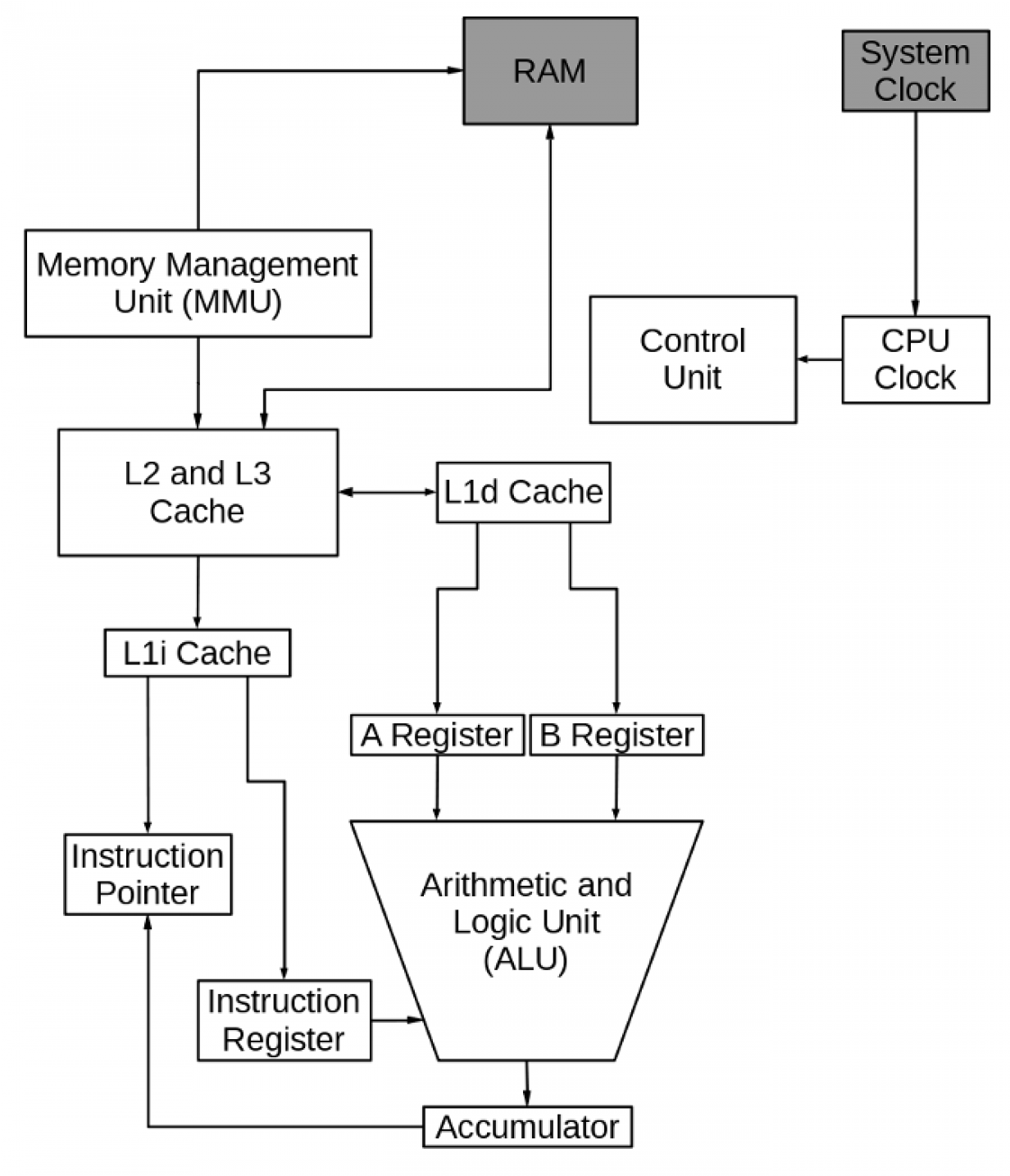

Components of CPU

CPU的簡單結構圖。灰色的部分並非CPU內部組成,只是方便關聯。

Arithmetic logic unit(算術邏輯單元) >The arithmetic logic unit (ALU) performs the arithmetic and logical functions that are the work of the computer. The A and B registers hold the input data, and the accumulator receives the result of the operation. The instruction register contains the instruction that the ALU is to perform.算術邏輯單元負責算術和邏輯運算。

Instruction register and pointer >The instruction pointer specifies the location in memory containing the next instruction to be executed by the CPU. When the CPU completes the execution of the current instruction, the next instruction is loaded into the instruction register from the memory location pointed to by the instruction pointer. 指令指針指向Memory中下一條要執行的指令位置,CPU結束當前指令運作後,將下一條指令由指令指針位置載入到指令暫存器。

Cache

The CPU never directly accesses RAM. Modern CPUs have one or more layers of cache. The CPU's ability to perform calculations is much faster than the RAM's ability to feed data to the CPU. 為了解決CPU運算速度和Memory存取速度之間的鴻溝,用cache作為中間橋樑加速資料存取。

Memory management unit

The memory management unit (MMU) manages the data flow between the main memory (RAM) and the CPU. MMU管理CPU與memory之間的數據流通。

CPU clock and control unit

All of the CPU components must be synchronized to work together smoothly. The control unit performs this function at a rate determined by the clock speed and is responsible for directing the operations of the other units by using timing signals that extend throughout the CPU. 所有的CPU組件由CU進行同步運作,而同步的rate由CPU clock決定。

X86暫存器

https://en.wikibooks.org/wiki/X86_Assembly/X86_Architecture

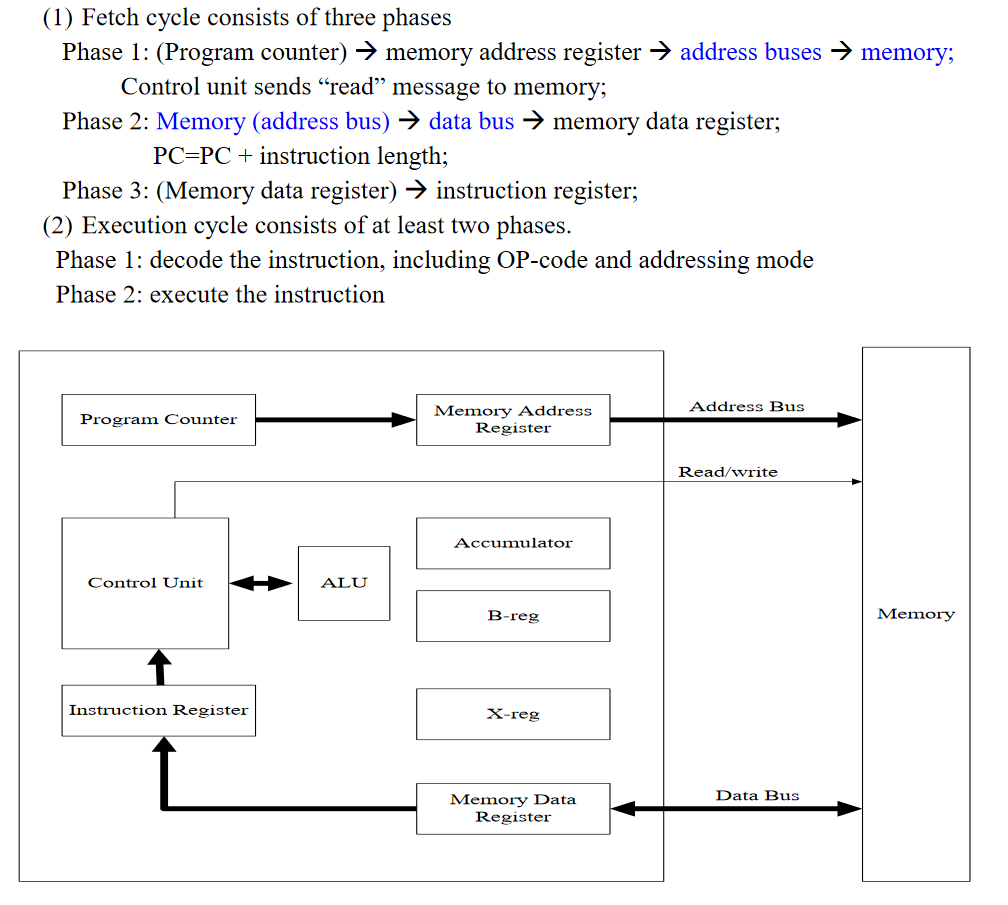

Instruction Cycle

Addressing Mode

這部分內容整理有點多TODO

中斷類型(8086):

Hardware Interrupts

Hardware interrupts are those interrupts which are caused by any peripheral device by sending a signal through a specified pin to the microprocessor. There are two hardware interrupts in 8086 microprocessor. They are:

- NMI (Non Maskable Interrupt) – It is a single pin non maskable hardware interrupt which cannot be disabled. It is the highest priority interrupt in 8086 microprocessor. After its execution, this interrupt generates a TYPE 2 interrupt. IP is loaded from word location 00008 H and CS is loaded from the word location 0000A H.

- INTR (Interrupt Request) – It provides a single interrupt request and is activated by I/O port. This interrupt can be masked or delayed. It is a level triggered interrupt. It can receive any interrupt type, so the value of IP and CS will change on the interrupt type received.

Software Interrupts

These are instructions that are inserted within the program to generate interrupts. There are 256 software interrupts in 8086 microprocessor. The instructions are of the format INT type where type ranges from 00 to FF. The starting address ranges from 00000 H to 003FF H. These are 2 byte instructions. IP is loaded from type * 04 H and CS is loaded from the next address give by (type * 04) + 02 H. Some important software interrupts are:

- TYPE 0 corresponds to division by zero(0).

- TYPE 1 is used for single step execution for debugging of program.

- TYPE 2 represents NMI and is used in power failure conditions.

- TYPE 3 represents a break-point interrupt.

- TYPE 4 is the overflow interrupt.

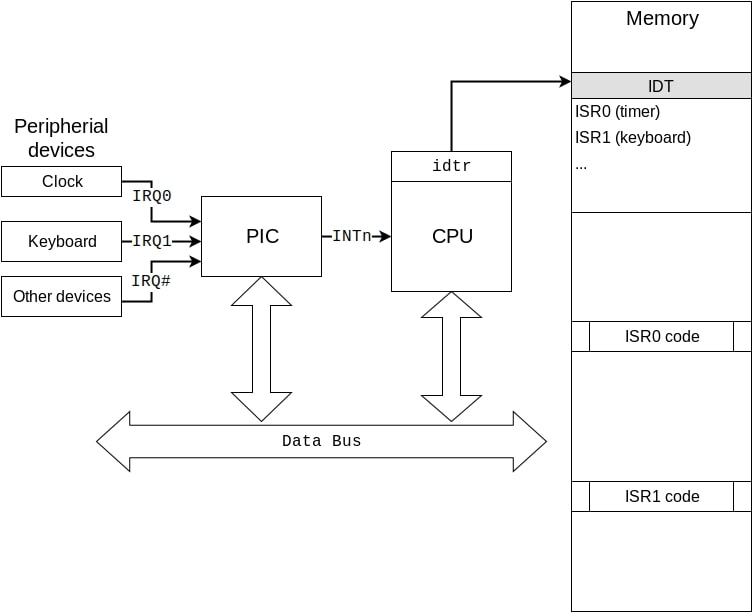

中斷處理流程 (thx to Alex Dzyoba)

TODO

Programmable Interrupt Controller (PIC)

Interrupt Descriptor Table (IDT)

什麽是IDT: >Interrupt descriptor table (IDT) is an x86 system table that holds descriptors for Interrupt Service Routines (ISRs) or simply interrupt handlers.

IDT與IVT(interrupt vector table)區別:

Interrupt Service Routines (ISRs)

Polling

輪詢(Polling)是一種CPU決策如何提供週邊裝置服務的方式,又稱「程式控制輸入輸出」(Programmed I/O)。輪詢法的概念是:由CPU定時發出詢問,依序詢問每一個週邊裝置是否需要其服務,有即給予服務,服務結束後再問下一個週邊,接著不斷週而復始。

參考

- https://www.redhat.com/sysadmin/cpu-components-functionality

- https://alex.dzyoba.com/blog/os-interrupts/

- https://www.geeksforgeeks.org/interrupts-in-8086-microprocessor/

- Wikipidea